### EMC Event Sept 2023

### PCB Topics and Tips for Better EMI and SI Performance

John Severson, PE ESDI

© 2023 ESDI

- John R. Severson, PE

- President and Principal Engineer, ESDI

- 35+ years designing electronic circuits, systems PC boards, RF, Design for EMC, and software

- Broad experience in many markets

- Military Electronics

- Analog/Digital Instrumentation, Metrology

- Medical Image processing and graphics

- CCTV, Analog and digital audio, video and security

- Adaptive technology for persons with disabilities

- Agricultural IoT, specialty RFID, and RF modules

- John Severson, PE 30 years designing electronic systems and PC boards

- PCBs with high speed logic, precision mixed signal, wireless, video, CCD/digital imaging, graphics, LCD display monitor controllers

- Embedded Microcontrollers and Linux Software

- Design for EMC, RF Modules integration, RFID systems

- SolidWorks (3D) and Altium Designer

## PCB Topics and Tips for Better EMI and SI Performance

- The focus of this presentation is on some key issues to improve performance of PCB layouts from an EMI, Signal (and power) Integrity perspective.

- There are many commonalities, and often following the tips for EMI can improve SI and vice-versa.

- PI is a win for both, and for board performance and reliability in general

- Some Practical Tips

### EMI / EMC Issues

- EMI requires both a noise source and an antenna.

- **Digital signals** and **switching power** supplies have **high** harmonic content.

- EMI problems are most often from common mode noise

- Crosstalk noise from a source can couple onto a potential antenna

- Ground or Power Bounce lead to common mode noise

- For **EMI**, **uA** and **uV** can be problematic. **Immunity** can encounter **A** and **kV** levels.

### SI - Signal Integrity Issues

- **Distortion** Attenuation, Noise, Timing distortion, Bandwidth limiting -- Parasitics

- Reflections (impedance discontinuities)

- Crosstalk between signals affects data and timing

- Ground or Power Bounce distort signals and timing

- Power supply distribution issues or collapse

- Interference (Self and System EMC)

# Some EMI and SIPI Issues in Common

- The **Hidden Schematic** real parts have parasitics

- Fast Rise Times and High Clock Speeds magnify the issues

- Impedance discontinuities (and failure to control the return path) reduce SI and increase EMI

- Poor and Inadequate Power Bypassing reduce SI and increase EMI

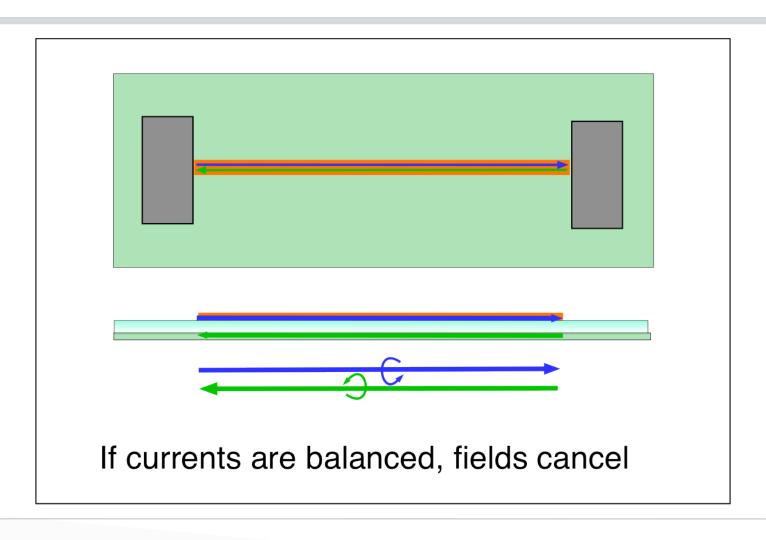

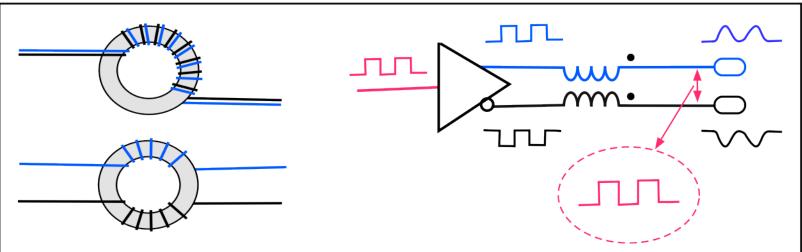

- Balancing (differential) improves both SI and EMI

## Some EMI and SI Divergent Issues

- EMI Filters limit bandwidth to reduce harmonics Can reduce signal integrity if too aggressive

- A few mV of noise is unlikely to cause SI issues, but a few uV of noise can cause an EMI failure.

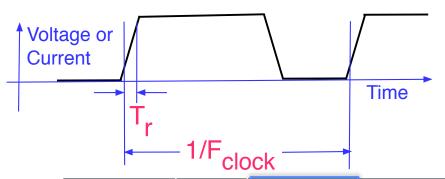

- Faster Rise Times are needed for high data rates but also significantly increase problematic harmonics for EMI

- (My observation is that SI is generally more easily modeled and simulated than EMI)

# Frequency, Wavelength, and the Time Domain

•  $\lambda = 300/f(MHz)$  in meters (in air)

- $\lambda$  is less in PCB  $\sim \frac{1}{\sqrt{\epsilon_r}}$

- Consider the design at DC 1MHz 100MHz 1GHz etc.

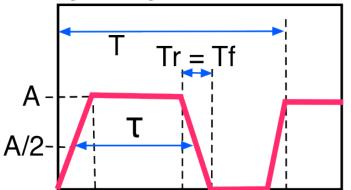

- The maximum spectrum from a digital signal can be estimated

Digital Signal Time domain

Frequency domain (bounds)

### Rise Time, Frequency and Scale

**Critical Len** is distance where Tprop is < 20% of Trise

$\lambda/20$  is a conservative estimate of "electrically small"

| Clock<br>Frequency | Rise<br>Time<br>(1/10) | Critical<br>Len* (in)<br>FR4 | Wavelen<br>λ (m)<br>Air | 10 <sup>th</sup> Harm | λ/10<br>(m)<br>Air | λ/20<br>(in)<br>FR4 |

|--------------------|------------------------|------------------------------|-------------------------|-----------------------|--------------------|---------------------|

| 1 MHz              | 100nS                  | 100                          | 300 m                   | 10 MHz                | 30 m               | 290                 |

| 10 MHz             | 10nS                   | 10                           | 30 m                    | 100 MHz               | 3 m                | 29                  |

| 100 MHz            | 1nS                    | 1                            | 3 m                     | 1 GHz                 | 30 cm              | 2.9                 |

| 1 GHz              | 100pS                  | 0.1                          | 30 cm                   | 10 GHz                | 3 cm               | 0.29                |

| 10 GHz             | 10pS                   | 0.01                         | 3 cm                    | 100 GHz               | 3 mm               | 0.029               |

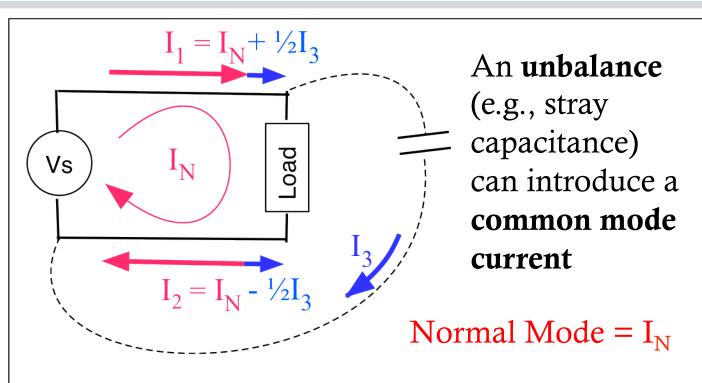

#### Normal and Common Mode

Common Mode =  $I_{CM} = \frac{1}{2}I_3$

I<sub>CM</sub> reduces **signal integrity** and causes **EMI**

# Crosstalk and Coupling Mechanisms

• Capacitive (Electric Field)

• Inductive (Magnetic Field)

• Common (Shared) Impedance

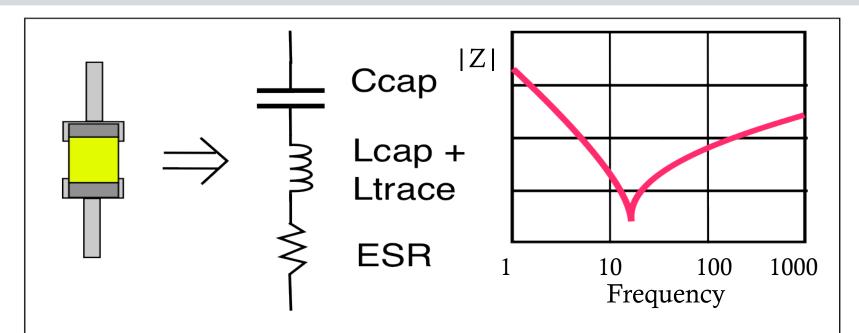

# Simplified Real Component Model for SMT ceramic capacitors

Parasitic characteristics of capacitor and trace/ via. The graph shows a sample "self-resonance" where impedance rises after hitting a minimum.

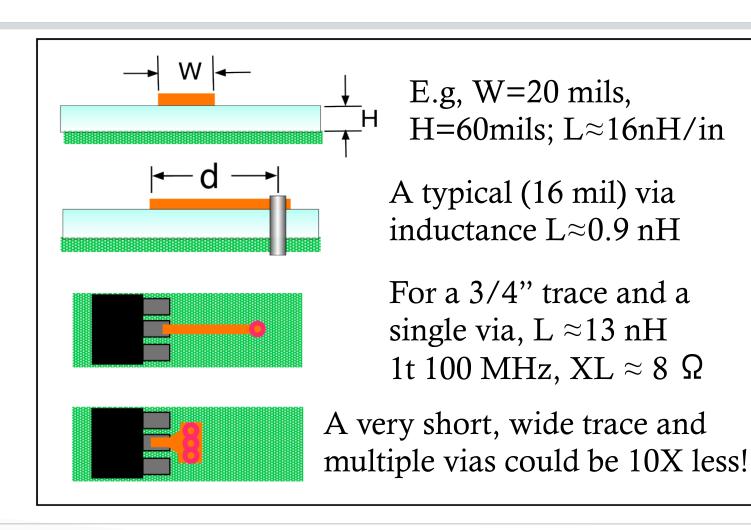

### Trace and Via RF Impedance

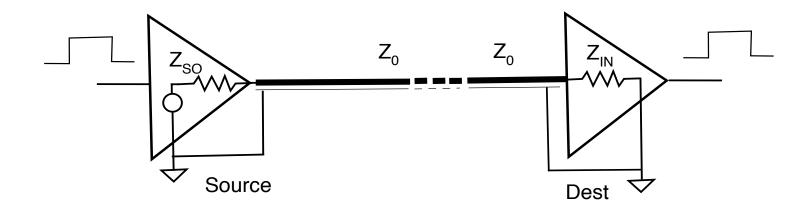

### Quick Review - Transmission Lines, Terminations and Reflections

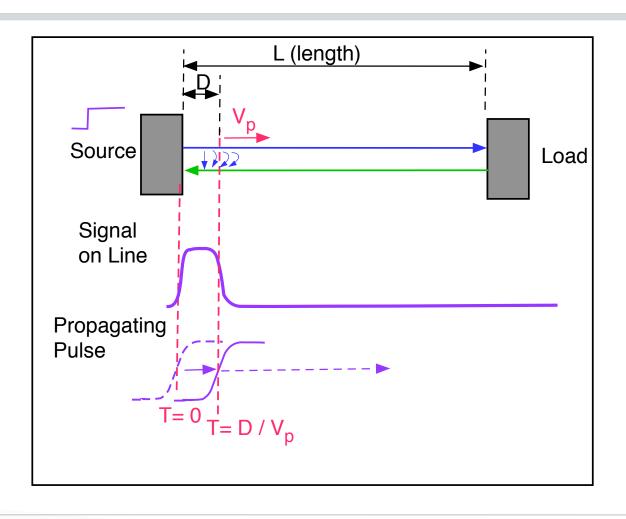

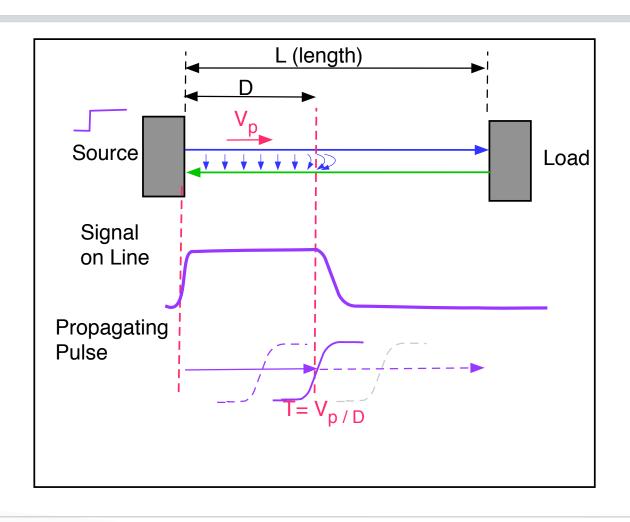

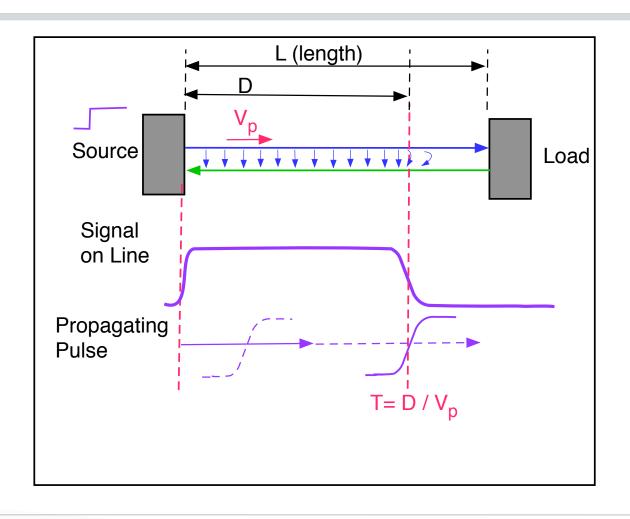

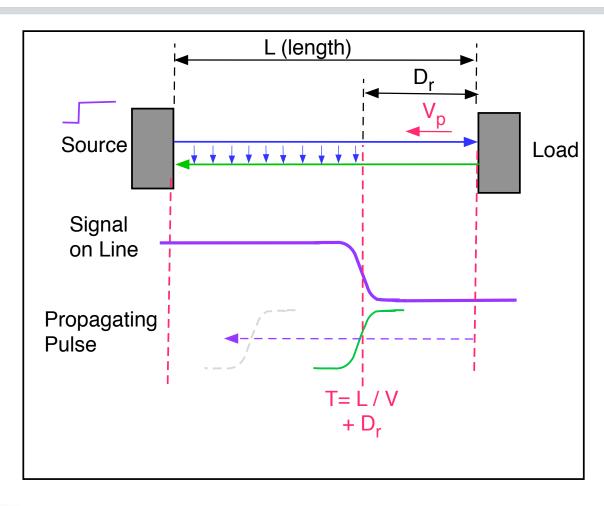

### Transmission Line propagation

#### Pulse travels down the line...

### Building field as it propagates...

When it arrives at the end, a reflection occurs it there is an impedance mismatch.

Zload = Zo

• No reflection

Zload > Zo

• Positive reflection

Zload < Zo

• Negative reflection

Reflection is  $\rho = (Z-Zo)/(Z+Zo)$

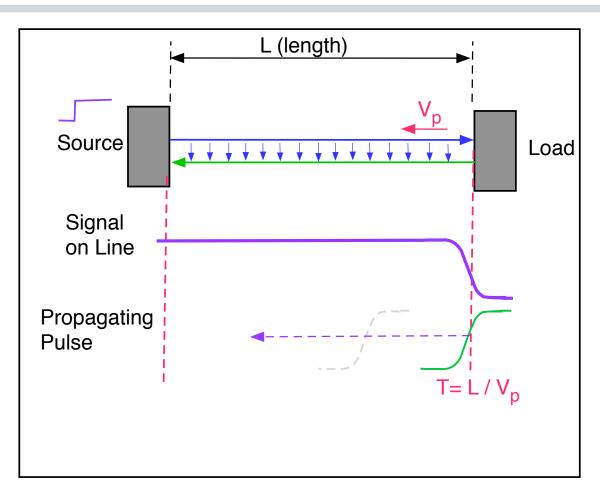

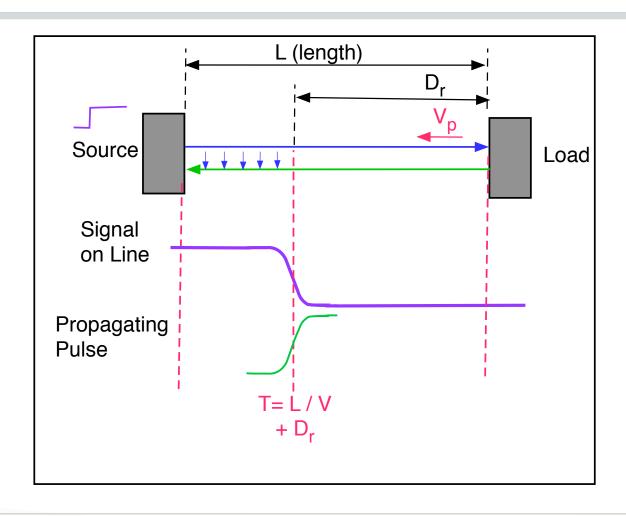

### The Reflected pulse travels back toward the source, altering the field as it goes

Zload < Zo

• Negative reflection

(this example pulse is for a short Z=0)

### The Reflected Pulse Propagates back toward the Source...

This example shows a negative going pulse since the load was low Z.

What if the source was low Z and the load High Z...

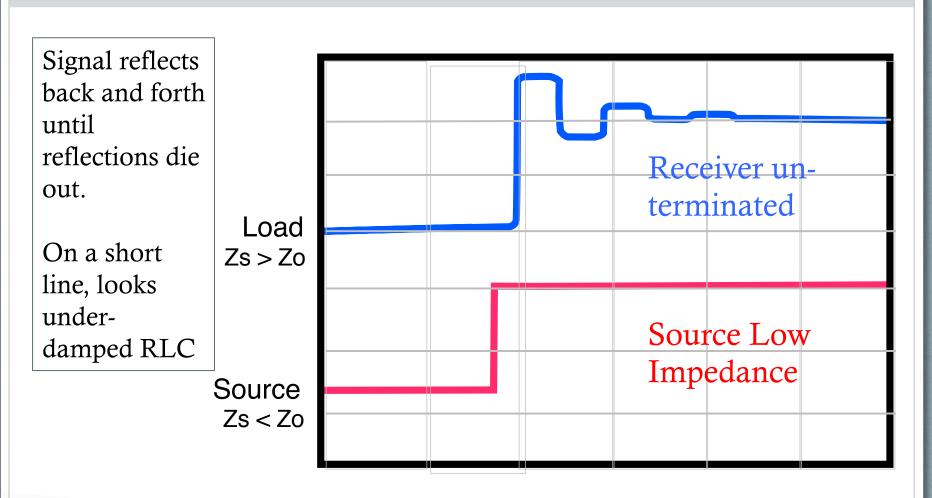

# Impedance Discontinuities can look like "Ringing"

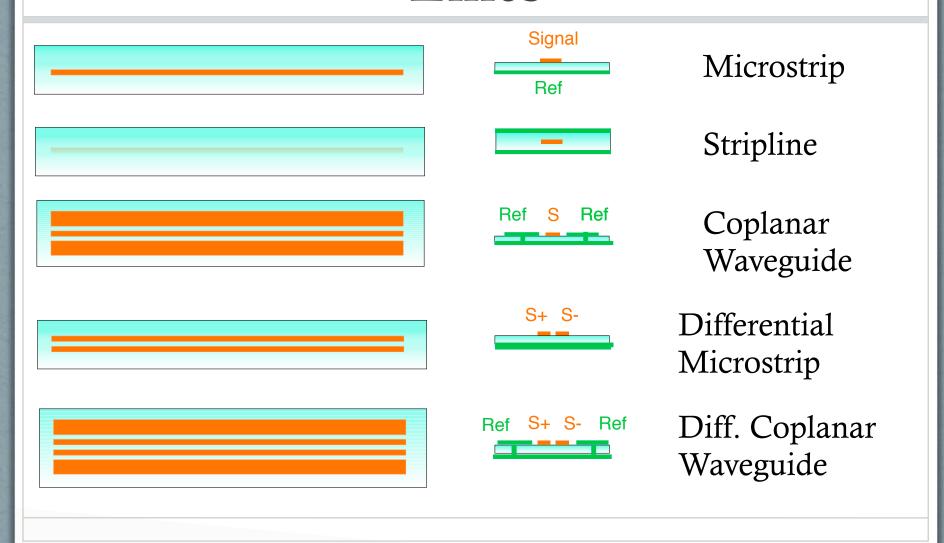

### Common Planar Transmission Lines

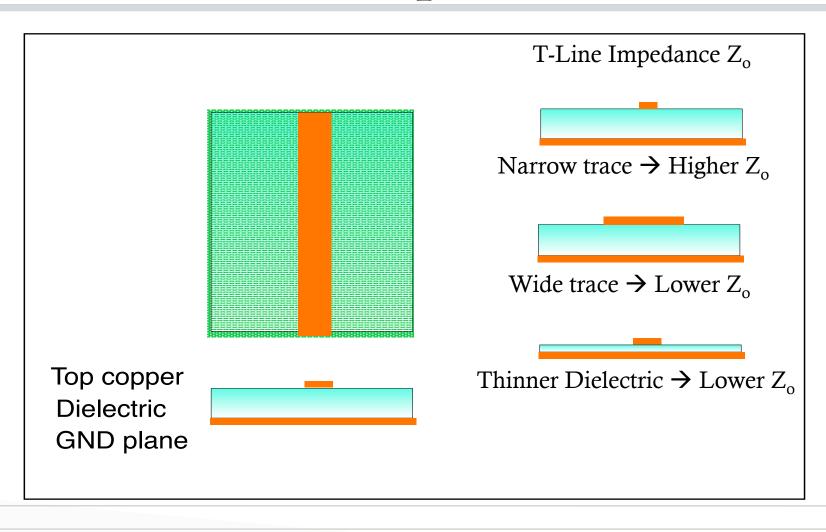

# Trace over GND Plane – the Microstrip T-Line

### Trace Impedance

- Reasonable approximate formulas exist for Microstrip and Striplines.

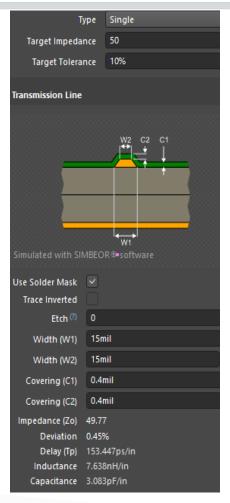

- Use of a 2D field solver is much better and is highly recommended Built into Altium *Designer*.

- There are online 2D solver options.

### 2D Field Solver Example

From Altium Designer 2023 built into layer stack manager

| Simulated with SIMBEOR® software |                       |   |                |               |             |             |        | Die       |     |

|----------------------------------|-----------------------|---|----------------|---------------|-------------|-------------|--------|-----------|-----|

|                                  |                       | # | Name           | Material      |             | Туре        | Weight | Thickness | Dk  |

| Use Solder Mask                  | $\checkmark$          |   | Top Overlay    |               |             | Overlay     |        |           |     |

| Trace Inverted                   |                       |   | Top Solder     | Solder Resist |             | Solder Mask |        | 0.4mil    | 3.5 |

| Etch <sup>(?)</sup>              | 0                     | 1 | Top Layer      |               | <b>(10)</b> | Signal      | 1oz    | 1.4mil    |     |

| Clearance (S)                    | 5mil                  |   | Dielectric 4   | PP-013        | <u></u>     | Prepreg     |        | 3.8mil    | 4.3 |

| Width (W1)                       | 30.23mil              |   | Dielectric 2   | PP-016        | <u></u>     | Prepreg     |        | 4.6mil    | 4.4 |

| Width (W2)                       | 30.23mil              | 2 | Layer 1        | CF-004        | <u></u>     | Plane       | 1oz    | 1.378mil  |     |

| Covering (C1)                    | 0.4mil                |   | Dielectric 1   | Core-042      |             | Core        |        | 39mil     | 4.6 |

| Covering (C2)                    | 0.4mil                |   | Layer 2        | CF-004        |             | Plane       | 1oz    | 1.378mil  |     |

| Trace Gap (G)                    | 5mil                  |   | Dielectric 3   | PP-016        |             | Prepreg     |        | 4.6mil    | 4.4 |

|                                  | 50.02                 |   | Dielectric 5   | PP-013        |             | Prepreg     |        | 3.8mil    | 4.3 |

|                                  | 0.03%<br>147.687ps/in | 4 | Bottom Layer   |               |             | Signal      | 1oz    | 1.4mil    |     |

| 2111                             | 7.387nH/in            |   | Bottom Solder  | Solder Resist |             | Solder Mask |        | 0.4mil    | 3.5 |

| Capacitance                      | 2.953pF/in            |   | Bottom Overlay |               |             | Overlay     |        |           |     |

### PC Board Stack-up

- Good **PCB Stack Up** is a **must do** starting point for **good EMI and SI** performance

- Think of the **stackup** as the **foundation**, like for building

- Most important is clean reference (gnd) planes. They are essential for low return impedance, controlled impedance traces, effective bypassing, minimizing ground bounce, and reducing common mode noise.

- All **high speed routes** should be over an **uninterrupted reference plane**.

# Avoid Impedance Discontinuities!

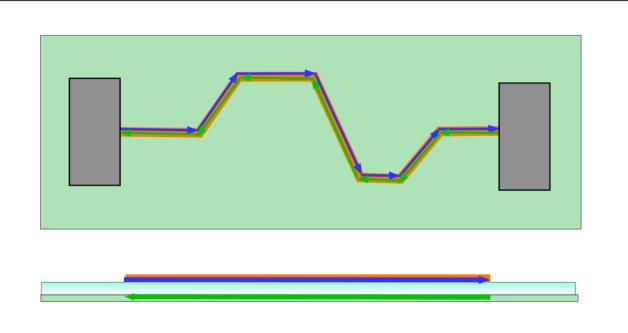

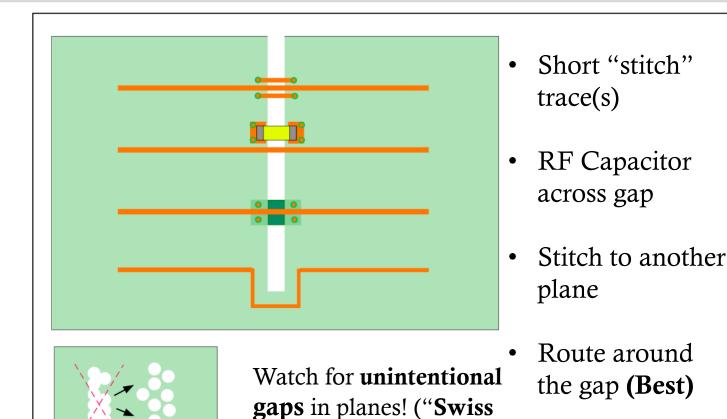

- **Routing** over a **gap** in the **plane** or a "**Swiss Cheese**" Reference Plane

- Changing Reference Planes (e.g., via to another layer)

- A **change** of **line width** on the same layer

- Stubs

- Un-terminated Transmission Lines

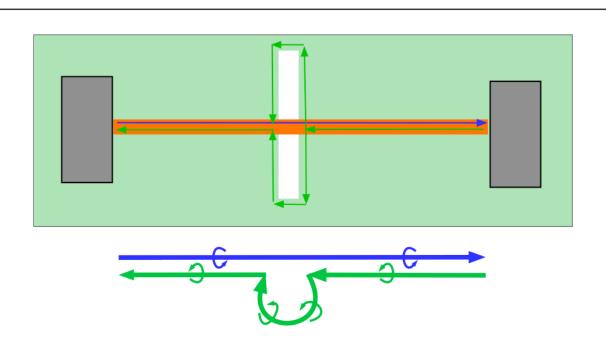

### Trace over continuous ground plane – Microstrip – RF return current follows signal

### Trace over continuous ground plane – Microstrip – RF return current follows signal

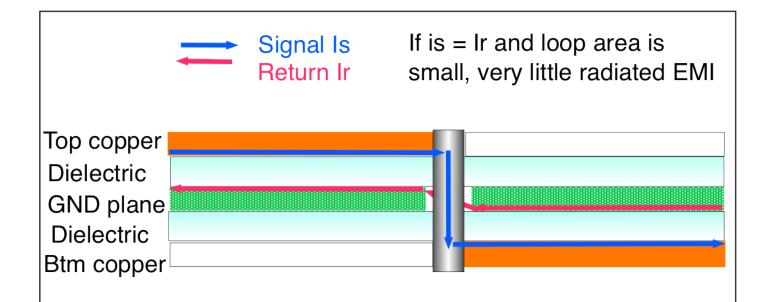

At RF Frequencies, the return current (in the ground plane) closely follows the signal path, so long as the ground plane is *continuous*.

### Trace over discontinuous ground plane -- routing over gaps!

A large loop is created, currents are no longer balanced, and a common mode current is introduced in the ground plane.

### ...Even worse with isolated planes

The return current **will** find a way back to the source, e.g., through stray capacitance. A significant antenna may be created.

### Create a low impedance path for RF return currents

Cheese" Plane)

### Changing Reference Planes

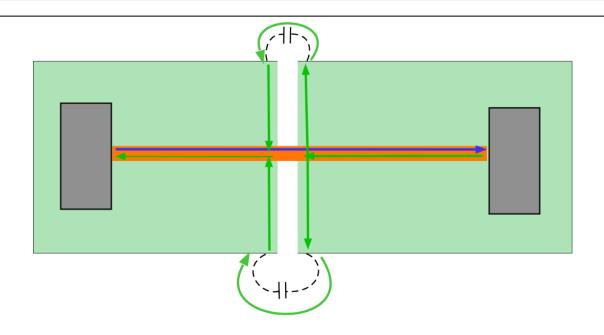

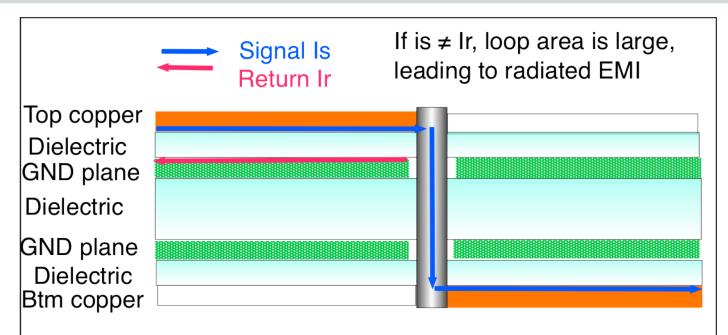

Case 1: Signal is via'd from one side of a reference plane to the other side of the -- OK as the return path is continuous and can closely follow signal

### Changing Reference Planes

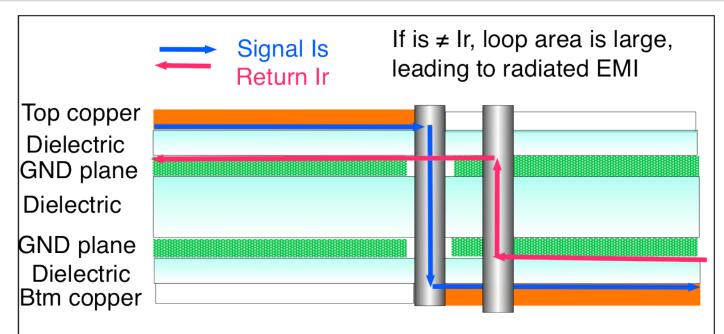

**Case 2**: Signal is via'd from one side of a reference plane to a separate reference plane. This is a problem as the **ground is not continuous**.

### Changing Reference Planes

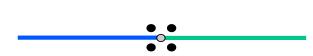

Case 2: Solution: Add GND via(s) between the reference planes adjacent to the signal via to provide a low RF impedance for the return. – Even better – quad via surround of signal

### Isolated (e.g., power) Reference Planes

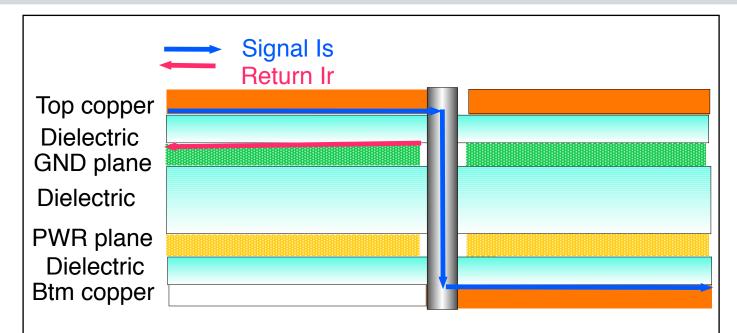

**Case 3**: Signal is via'd from a ground reference plane to an isolated (e.g., power) plane... No low impedance path for the RF return current.

### Isolated (e.g., power) Reference Planes

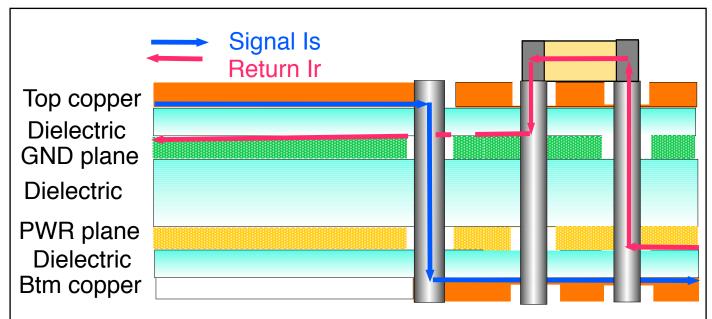

Case 3: A small capacitor near the signal via with very low RF impedance to both planes (e.g., power and ground) provides a significantly improved return current path.

### Some Tips

- Keep stubs after terminators very short

- Route through and terminate after pins for higher speed signals

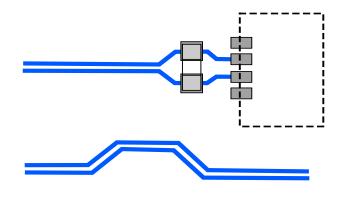

- Route pairs in a balanced manor

- Use on-chip termination for very high speed signals

• Even better: Use a Quad Via pattern

### Summary: Avoiding the Discontinuous Ground Issues

- Use Ground Plane(s). If possible, avoid gaps in it.

- Don't route across gaps in planes or change reference planes without ensuring a low RF impedance path at or near the via.

- Most important for **high rise-time**, **high duty cycle**, but **all** signals can cause EMI!

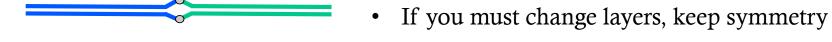

- Route **high speed traces** and **differential pairs** on a **single layer** if possible.

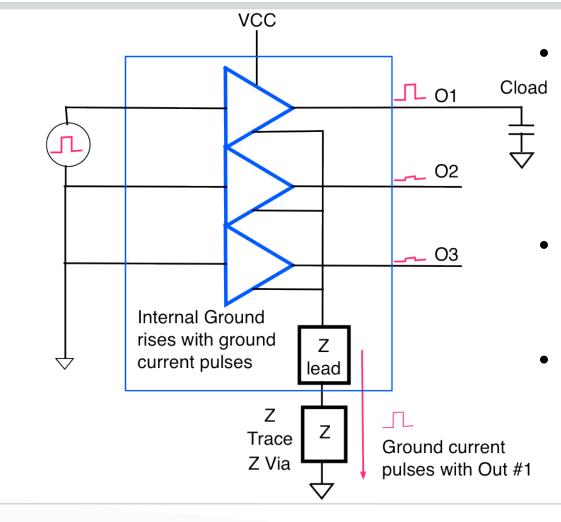

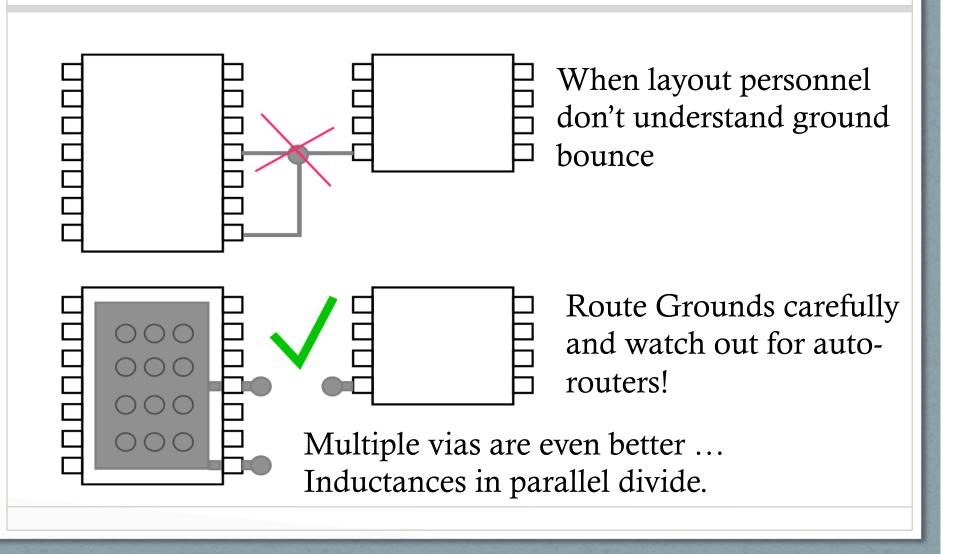

## High Ground Impedance and Ground Bounce

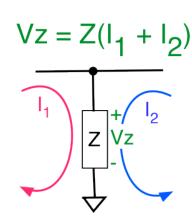

Switching currents are coupled to other outputs through common impedance

- Low speed signals still can contain RF

- Must keep ground impedance low!

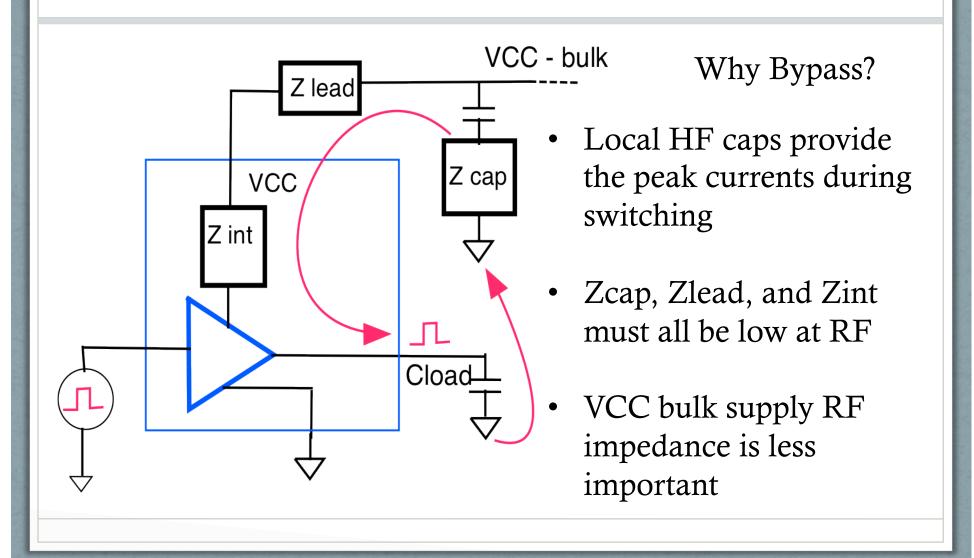

### Good Bypass is Essential

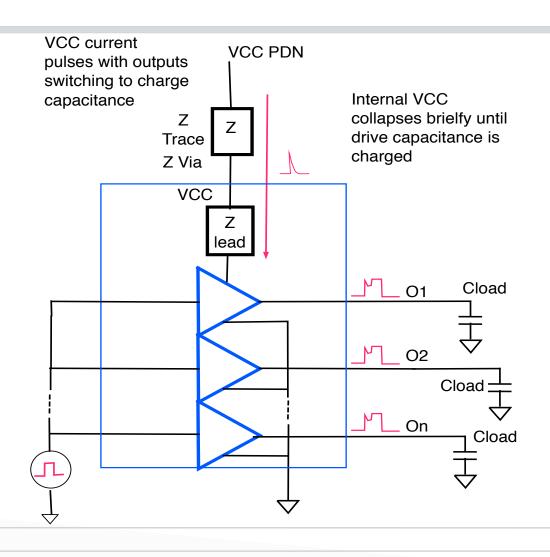

# 4. High PDN Impedance and Power Bounce

- Switching currents are coupled to outputs From VCC.

- Low speed signals still can contain RF

- Must keep PDN impedance low!

- Bypass Caps

Essential

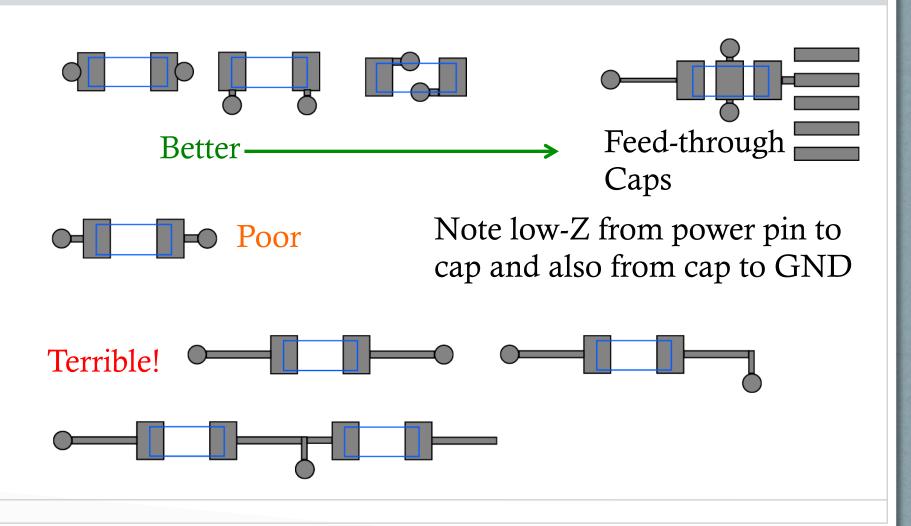

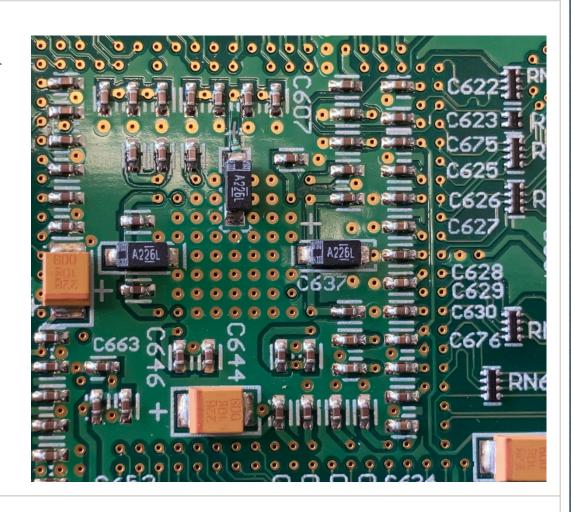

# Bypass Layout for lower RF Impedance

#### Avoid this common error!

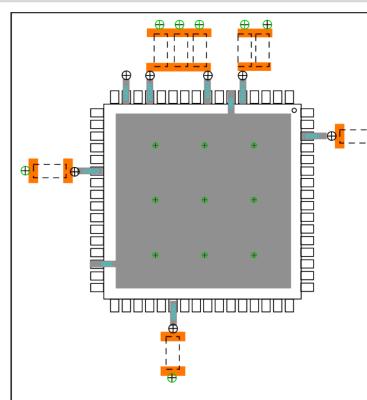

### Practical chip example – Bypass caps on opposite side

(Based on a Reference Design)

- Ground area under chip and return GND pins to this.

- Stitch all ground vias to the continuous ground plane.

- Make a supplemental ground plane where practical on the bottom layer.

- Power fed from internal planes.

# Another Example BGA (caps un bottom side)

- Shortest practical route from BGA pads to Via to Caps.

- Cap immediately Returned to GND under BGA.

- GND Vias include inner GND plane and bottom side GND fill.

- Via in pad option was not available for this, but would reduce inductance.

### Tips for Bypass, Ground and Power Bounce

#### Minimize Ground and Power Inductance

- Never share ground vias or traces. In fact use multiple vias. Via inductances in parallel reduce the total.

- Keep ground traces **short and fat** (3:1)

- Use a **continuous ground plane close to the routing layer** and use very **low impedance paths** for bypass caps

- TIP: Use series impedance on outputs or IO to reduce peak current spikes.

- Remember the *ALL* outputs can be affected by ground and power bounce... not just the "fast" signals.

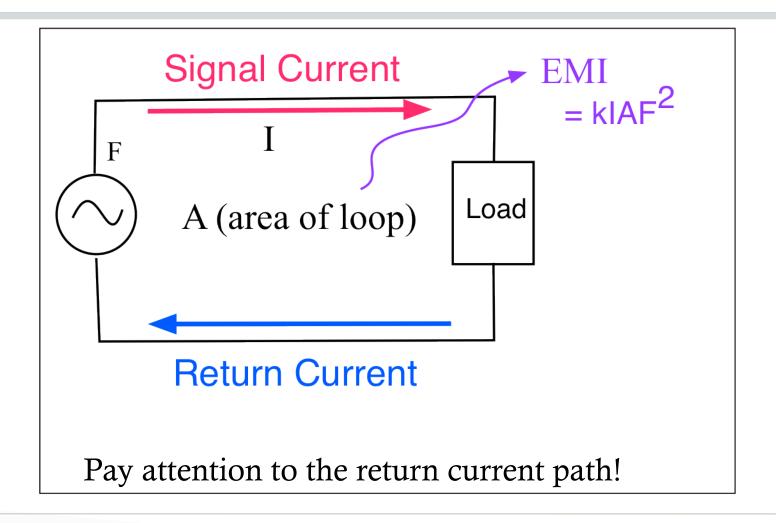

### EMI: Minimize the loop area

#### For EMI - Shield or Filter All IO

- Every signal entering or exiting must be shielded or filtered (or both)

- **Shielded** Cables **must** connect connector shield to shield enclosure

- **Unshielded** cables (including shielded cables in a non-shielded enclosure) **must** Filter!

- Need to keep common mode noise off cables

- Need to provide low RF impedance signal return paths – small loop areas

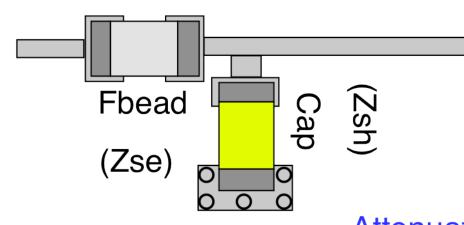

# Example – add a series ferrite and a shunt capacitor

Typical Ferrite: 100 ohms at 100 MHz

Cap 0.001 uF: 1.6 ohms at 100 MHz

Attenuation ≈ 1.6/100 - about 36 dB

(neglecting trace impedance and esr)

### Some options for RF filtering IO

- Series Impedance

- Ferrite or Resistor

Tee or Pi 3-terminal Filter, F-T Cap

Common Mode Choke

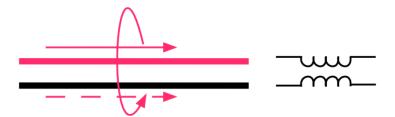

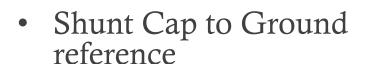

### Common Mode Chokes

- Two windings share magnetic field

- Fields cancel for Normal Mode – Low Z

- Fields add for Common Mode – High Z

- Differential (Normal) signal OK

- Common mode is blocked

- No Ground Needed

### Summing up...

- Remember the "Hidden Schematic"

- Start with a **good PCB Stack up** plan -- Pay particular attention to a **solid ground (reference plane)** structure

- Avoid Impedance and Return Path Discontinuities

- Pay close attention to return currents and return current paths. Don't unbalance balanced lines.

### Summing up...

- Identify high speed lines and give them priority.

- Highest speed on single layer

- Keep **Differential lines** together and **balanced**.

- Take great care in bypassing to keep series impedance at RF very low.

- Group (if possible) and Filter all IO

### Questions?

Thank You!

Stop by the ESDI table for more Info

6110 Blue Circle Drive, Ste. 245 Minnetonka, MN 55345

John R. Severson, PE 952-935-9459 js@esdimn.com <u>esdimn.com</u>

PCB Layout Topics and Tips for Improved EMI and Signal Integrity performance © 2023 ESDI

- The content of this presentation is informational only and intended to provide general guidance. It is provided as-is.

- Use in any particular design is the responsibility of the designer and ESDI cannot guarantee accuracy and assumes no risk or liability whatsoever for its use.